October 1987 Revised January 1999

## MM74C89

# 64-Bit 3-STATE Random Access Read/Write Memory

### **General Description**

The MM74C89 is a 16-word by 4-bit random access read/write memory. Inputs to the memory consist of four address lines, four data input lines, a write enable line and a memory enable line. The four binary address inputs are decoded internally to select each of the 16 possible word locations. An internal address register latches the address information on the positive to negative transition of the memory enable input. The four 3-STATE data output lines working in conjunction with the memory enable input provide for easy memory expansion.

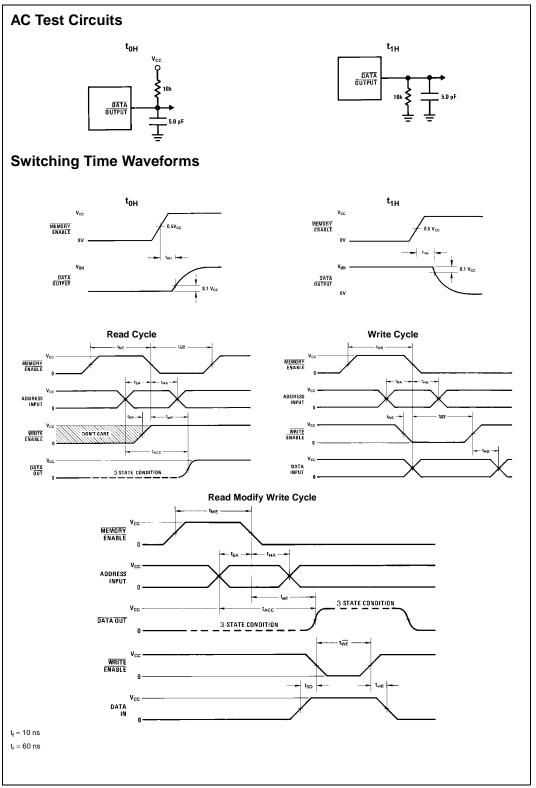

**Address Operation:** Address inputs must be stable  $t_{SA}$   $\underline{prior}$  to the positive to negative transition of  $\overline{memory}$   $\underline{enable}$ . It is thus not necessary to hold address information stable for more than  $t_{HA}$  after the memory is enabled (positive to negative transition of  $\overline{memory}$   $\underline{enable}$ ).

Write Operation: Information present at the data inputs is written into the memory at the selected address by bringing write enable and memory enable LOW.

**Read Operation:** The complement of the information which was written into the memory is non-destructively read out at the four outputs. This is accomplished by selecting the desired address and bringing memory enable LOW and write enable HIGH.

When the device is writing or disabled the output assumes a 3-STATE (Hi-z) condition.

### **Features**

- Wide supply voltage range: 3.0V to 15V

- Guaranteed noise margin: 1.0V

- $\blacksquare$  High noise immunity: 0.45  $\rm V_{CC}$  (typ.)

- Low power TTL compatibility: fan out of 2 driving 74L

- Low power consumption: 100 nW/package (typ.)

- Fast access time: 130 ns (typ.) at V<sub>CC</sub> = 10V

- 3-STATE output

Note: The timing is different than the DM7489 in that a positive to negative transition of the memory enable must occur for the memory to be selected.

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                    |

|--------------|----------------|------------------------------------------------------------------------|

| MM74C89N     | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide |

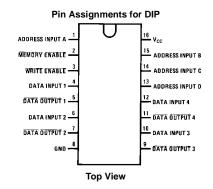

### **Connection Diagram**

### **Truth Table**

| ME | WE | Operation        | Condition of Outputs        |  |  |

|----|----|------------------|-----------------------------|--|--|

| L  | L  | Write            | 3-STATE                     |  |  |

| L  | Н  | Read             | Complement of Selected Word |  |  |

| Н  | L  | Inhibit, Storage | 3-STATE                     |  |  |

| Н  | Н  | Inhibit, Storage | 3-STATE                     |  |  |

# Logic Diagram DATA <u>DATA</u> DATA <u>DATA</u> DATA <u>DATA</u> DATA <u>DATA</u> INPUT 1 OUTPUT 1 INPUT 2 OUTPUT 2 INPUT 3 OUTPUT 3 INPUT 4 OUTPUT 4 INPUT B -> ADDRESS DECODER INPUT B 🔫

# **Absolute Maximum Ratings**(Note 1)

$\begin{array}{lll} \mbox{Voltage at any Pin} & -0.3\mbox{V to V}_{\mbox{CC}} + 0.3\mbox{V} \\ \mbox{Operating Temperature Range} & -40\mbox{°C to } + 85\mbox{°C} \\ \mbox{Storage Temperature Range } (T_{\mbox{S}}) & -65\mbox{°C to } + 150\mbox{°C} \\ \end{array}$

Power Dissipation (P<sub>D</sub>)

$\begin{array}{cc} \text{Dual-In-Line} & 700 \text{ mW} \\ \text{Small Outline} & 500 \text{ mW} \\ \text{Operating V}_{\text{CC}} \text{ Range} & 3.0 \text{V to } 15 \text{V} \\ \end{array}$

Absolute Maximum  $V_{CC}$  18V Lead Temperature ( $T_L$ ) (Soldering, 10 seconds) 260°C

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

### **DC Electrical Characteristics**

Min/Max limits apply across temperature range, unless otherwise noted

| Symbol              | Parameter                      | Conditions                               | Min                   | Тур    | Max | Units |

|---------------------|--------------------------------|------------------------------------------|-----------------------|--------|-----|-------|

| CMOS TO             | CMOS                           |                                          |                       |        | I   | 1     |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage      | V <sub>CC</sub> = 5.0V                   | 3.5                   |        |     | V     |

|                     |                                | $V_{CC} = 10V$                           | 8.0                   |        |     | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage      | V <sub>CC</sub> = 5.0V                   |                       |        | 1.5 | V     |

|                     |                                | V <sub>CC</sub> = 10V                    |                       |        | 2.0 | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage     | $V_{CC} = 5.0V, I_{O} = -10 \mu A$       | 4.5                   |        |     | V     |

|                     |                                | $V_{CC} = 10V$ , $I_O = -10 \mu A$       | 9.0                   |        |     | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage     | $V_{CC} = 5.0V, I_{O} = +10 \mu A$       |                       |        | 0.5 | V     |

|                     |                                | $V_{CC} = 10V$ , $I_{O} = +10 \mu A$     |                       |        | 1.0 | V     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current      | $V_{CC} = 15V, V_{IN} = 15V$             |                       | -0.005 | 1.0 | μА    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current      | $V_{CC} = 15V, V_{IN} = 0V$              | -1.0                  | -0.005 |     | μΑ    |

| I <sub>OZ</sub>     | Output Current in High         | V <sub>CC</sub> = 15V, V = 15V           |                       | 0.005  | 1.0 | μΑ    |

|                     | Impedance State                | $V_{CC} = 15V, V_{O} = 0V$               | -1.0                  | -0.005 |     | μΑ    |

| I <sub>CC</sub>     | Supply Current                 | V <sub>CC</sub> = 15V                    |                       | 0.05   | 300 | μΑ    |

| CMOS/LPT            | TL INTERFACE                   | •                                        |                       |        |     |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage      | V <sub>CC</sub> = 4.75V                  | V <sub>CC</sub> – 1.5 |        |     | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage      | V <sub>CC</sub> = 4.75V                  |                       |        | 0.8 | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage     | $V_{CC} = 4.75V$ , $I_{O} = -360 \mu A$  | 2.4                   |        |     | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage     | $V_{CC} = 4.75V$ , $I_{O} = +360 \mu A$  |                       |        | 0.4 | V     |

| OUTPUT D            | RIVE (See 54C/74C Family Chara | cteristics Data Sheet) (Short Circuit Cu | rrent)                |        |     |       |

| I <sub>SOURCE</sub> | Output Source Current          | $V_{CC} = 5.0V, V_{OUT} = 0V$            | -1.75                 | -3.3   |     | mA    |

|                     | (P-Channel)                    | T <sub>A</sub> = 25°C                    |                       |        |     |       |

| I <sub>SOURCE</sub> | Output Source Current          | $V_{CC} = 10V, V_{OUT} = 0V$             | -8.0                  | -15    |     | mA    |

|                     | (P-Channel)                    | T <sub>A</sub> = 25°C                    |                       |        |     |       |

| I <sub>SINK</sub>   | Output Sink Current            | $V_{CC} = 5.0V$ , $V_{OUT} = V_{CC}$     | 1.75                  | 3.6    |     | mA    |

|                     | (N-Channel)                    | $T_A = 25^{\circ}C$                      |                       |        |     |       |

| I <sub>SINK</sub>   | Output Sink Current            | $V_{CC} = 10V$ , $V_{OUT} = V_{CC}$      | 8.0                   | 16     |     | mA    |

|                     | (N-Channel)                    | $T_A = 25^{\circ}C$                      |                       |        |     |       |

# AC Electrical Characteristics (Note 2) $T_A = 25^{\circ}C, C_L = 50 \text{ pF}, \text{ unless otherwise noted}$

| Symbol                            | Parameter                        | Conditions                                   | Min | Тур | Max             | Units |

|-----------------------------------|----------------------------------|----------------------------------------------|-----|-----|-----------------|-------|

| t <sub>pd</sub>                   | Propagation Delay from           | V <sub>CC</sub> = 5V                         |     | 270 | 500             | ns    |

|                                   | Memory Enable                    | V <sub>CC</sub> = 10V                        |     | 100 | 220             | ns    |

| t <sub>ACC</sub>                  | Access Time from                 | V <sub>CC</sub> = 5V                         |     | 350 | 650             | ns    |

|                                   | Address Input                    | V <sub>CC</sub> = 10V                        |     | 130 | 280             | ns    |

| t <sub>SA</sub>                   | Address Setup Time               | $V_{CC} = 5V$                                | 150 |     |                 | ns    |

|                                   |                                  | $V_{CC} = 10V$                               | 60  |     |                 | ns    |

| t <sub>HA</sub>                   | Address Hold Time                | V <sub>CC</sub> = 5V                         | 60  |     |                 | ns    |

|                                   |                                  | $V_{CC} = 10V$                               | 40  |     |                 | ns    |

| t <sub>ME</sub>                   | Memory Enable Pulse Width        | V <sub>CC</sub> = 5V                         | 400 | 250 |                 | ns    |

|                                   |                                  | V <sub>CC</sub> = 10V                        | 150 | 90  |                 | ns    |

| t <sub>SR</sub>                   | Write Enable Setup               | $V_{CC} = 5V$                                | 0   |     |                 | ns    |

|                                   | Time for a Read                  | V <sub>CC</sub> = 10V                        | 0   |     |                 | ns    |

| t <sub>WS</sub>                   | Write Enable Setup               | V <sub>CC</sub> = 5V                         |     |     | t <sub>ME</sub> | ns    |

|                                   | Time for a Write                 | $V_{CC} = 10V$                               |     |     | t <sub>ME</sub> | ns    |

| t <sub>WE</sub>                   | Write Enable Pulse Width         | $V_{CC} = 5V, t_{WS} = 0$                    | 300 | 160 |                 | ns    |

|                                   |                                  | $V_{CC} = 10V, t_{WS} = 0$                   | 100 | 60  |                 | ns    |

| t <sub>HD</sub>                   | Data Input Hold Time             | V <sub>CC</sub> = 5V                         | 50  |     |                 | ns    |

|                                   |                                  | $V_{CC} = 10V$                               | 25  |     |                 | ns    |

| t <sub>SD</sub>                   | Data Input Setup                 | V <sub>CC</sub> = 5V                         | 50  |     |                 | ns    |

|                                   |                                  | V <sub>CC</sub> = 10V                        | 25  |     |                 | ns    |

| t <sub>1H</sub> , t <sub>0H</sub> | Propagation Delay from a Logical | $V_{CC} = 5V, C_L = 5 \text{ pF}, R_L = 10k$ |     | 180 | 300             | ns    |

|                                   | "1" or Logical "0" to the High   | $V_{CC} = 10V, C_L = 5 pF, R_L = 10k$        |     | -85 | 120             | ns    |

|                                   | Impedance State from             |                                              |     |     |                 |       |

|                                   | Memory Enable                    |                                              |     |     |                 |       |

| t <sub>1H</sub> , t <sub>0H</sub> | Propagation Delay from a Logical | $V_{CC} = 50V, C_L = 5 pF, R_L = 10k$        |     | 180 | 300             | ns    |

|                                   | "1" or Logical "0" to the High   | $V_{CC} = 10V, C_L = 5 pF, R_L = 10k$        |     | 85  | 120             | ns    |

|                                   | Impedance State from             |                                              |     |     |                 |       |

|                                   | Write Enable                     |                                              |     |     |                 |       |

| C <sub>IN</sub>                   | Input Capacity                   | Any Input (Note 3)                           |     | 5   |                 | pF    |

| C <sub>OUT</sub>                  | Output Capacity                  | Any Output (Note 3)                          |     | 6.5 |                 | pF    |

| C <sub>PD</sub>                   | Power Dissipation Capacity       | (Note 4)                                     |     | 230 |                 | pF    |

Note 2: AC Parameters are guaranteed by DC correlated testing.

Note 3: Capacitance is guaranteed by periodic testing.

Note 4: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation see Family Characteristics application note,

#### Physical Dimensions inches (millimeters) unless otherwise noted 0.740 - 0.780 0.090 (18.80 - 19.81)(2.286)15 14 13 12 11 10 [6] [15] [T INDEX AREA 0.250 ± 0.010 $(6.350 \pm 0.254)$ PIN NO. 1 PIN NO. 1 2 3 4 5 6 7 8 1 2 \_ IDENT IDENT OPTION 02 0.065 $\frac{0.130 \pm 0.005}{(3.302 \pm 0.127)}$ $\frac{0.060}{(1.524)}$ (1.651)4° TYP 0.300 - 0.320 OPTIONAL (7.620 **-** 8.128) 0.145 - 0.200 $\overline{(3.683 - 5.080)}$ 95°±5° $\frac{0.008 - 0.016}{(0.203 - 0.406)}$ TYP 90° ± 4° TYP 0.020 0.280 (0.508)0.125 - 0.150 (3.175 - 3.810) (7.112) MIN $(0.762 \pm 0.381)$ $\frac{0.014 - 0.023}{(0.356 - 0.584)}$ $0.100 \pm 0.010$ (0.325 +0.040 -0.015 $(2.540 \pm 0.254)$ 0.050 ± 0.010 (1.270 ± 0.254) N16E (REV F) TYP TYP

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com